Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

# SEVENTH FRAMEWORK PROGRAMME THEME

FET proactive 1: Concurrent Tera-Device Computing (ICT-2009.8.1)

**PROJECT NUMBER: 249013**

## **Exploiting dataflow parallelism in Teradevice Computing**

## D2.1 –Report on the reference set of applications chosen, and initial

## characterization of the applications

Due date of deliverable: 31<sup>st</sup> December 2010 Actual Submission: 31<sup>st</sup> December 2010

Start date of the project: January 1<sup>st</sup>, 2010 Duration: 48 months

**Lead contractor for the deliverable:** Barcelona Supercomputing Center (BSC)

Revision: See file name in document footer.

|       | Project co-founded by the European Commission                                         |  |  |

|-------|---------------------------------------------------------------------------------------|--|--|

|       | within the SEVENTH FRAMEWORK PROGRAMME (2007-2013)                                    |  |  |

| Disse | Dissemination Level: PU                                                               |  |  |

| PU    | Public                                                                                |  |  |

| PP    | Restricted to other programs participant (including the Commission Services)          |  |  |

| RE    | Restricted to a group specified by the consortium (including the Commission Services) |  |  |

| CO    | Confidential, only for members of the consortium (including the Commission Services)  |  |  |

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

## **Change Control**

| Version# | Author         | Organization | Change History                           |

|----------|----------------|--------------|------------------------------------------|

| 0.1      | Rosa M. Badia  | BSC          | Table of content                         |

| 0.2      | Rosa M. Badia  | BSC          | Editions in sections 2 and 3             |

| 0.3      | Yoav Etsion    | BSC          | Editions in sections 3 and 4             |

| 0.4      | Sylvain Girbal | Thales       | Input for sections 2, 3 and 4            |

| 0.5      | Antoni Portero | UNISI        | Input for section 3                      |

| 0.6      | Mikel Lujan    | UNIMAN       | Input for section 3 & section 4          |

| 1.0      | Rosa M. Badia  | BSC          | Integration of internal review and final |

|          |                |              | edition                                  |

## **Release Approval**

| Name           | Role                                              | Date       |

|----------------|---------------------------------------------------|------------|

| Rosa M. Badia  | Originator                                        |            |

| Nacho Navarro  | WP Leader                                         |            |

| Roberto Giorgi | <b>Project Coordinator for formal deliverable</b> | 31.12.2010 |

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

#### **TABLE OF CONTENTS**

| G   | LOSSARY         | ′                                                                          | 7      |

|-----|-----------------|----------------------------------------------------------------------------|--------|

| E   | XECUTIVE        | E SUMMARY                                                                  | 8      |

| 1   | INTRO           | DUCTION                                                                    | 9      |

|     | 1.1 Do          | OCUMENT STRUCTURE                                                          | 9      |

|     |                 | ELATION TO OTHER DELIVERABLES                                              |        |

|     | 1.3 Ac          | CTIVITIES REFERRED BY THIS DELIVERABLE                                     | 9      |

| 2   | IDENT           | IFICATION OF REFERENCE APPLICATIONS                                        | 10     |

|     | 2.1 CR          | RITERIA                                                                    | 10     |

|     | 2.2 KE          | ernels / Benchmarks                                                        | 11     |

|     | 2.3 Fu          | JLL APPLICATIONS                                                           | 12     |

|     | 2.3.1           | HiPEAC repository                                                          | 12     |

|     | 2.3.2           | Initial Reference Kernel/Application Disk Image                            | 12     |

| 3   | METO            | ODOLOGIES USED IN THE CHARACTERIZATION AND MODELING OF P                   | ROIFCT |

|     |                 | BENCHMARKS/APPLICATIONS                                                    |        |

| ••• |                 |                                                                            |        |

|     |                 | ARAMETERS TO BE MEASURED                                                   |        |

|     |                 | NALYTIC EVALUATION                                                         |        |

|     | 3.2.1           |                                                                            |        |

|     | 3.2.2<br>3.3 Ev | Task graph generation                                                      |        |

|     | 3.3.1           | ·                                                                          |        |

|     | 3.3.2           | •                                                                          |        |

|     | 3.3.3           |                                                                            |        |

|     | 3.3.4           |                                                                            |        |

|     | 3.3.5           | •                                                                          |        |

|     | 3.3.6           |                                                                            |        |

|     | 3.3.7           | ·                                                                          |        |

| _   |                 | ·                                                                          |        |

| 4   | INITIA          | L CHARACTERIZATION AND MODELING OF PROJECT KERNELS/BENCHMARKS/APPLICATIONS | 27     |

|     | 4.1 An          | NALYTIC EVALUATION                                                         |        |

|     | 4.1.1           |                                                                            |        |

|     | 4.2 Ev          | VALUATION USING PERFORMANCE/MONITORING TOOLS                               |        |

|     | 4.2.1           | ,                                                                          |        |

|     | 4.2.2           |                                                                            |        |

|     | 4.2.3           | ,                                                                          |        |

|     | 4.2.4           | , ,                                                                        |        |

|     | 4.2.5           | , , , ,                                                                    |        |

|     | 4.2.6           | Transactional Memory                                                       | 37     |

| 5   | CONCL           | LUSIONS                                                                    | 43     |

| D   | EEEDENC         | EC                                                                         | 44     |

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| FIGURE 1 EMS USAGE INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13            |

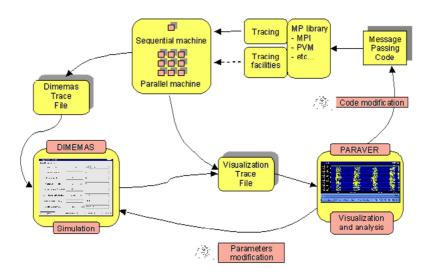

| FIGURE 2 CEPBA-TOOLS WORKFLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22            |

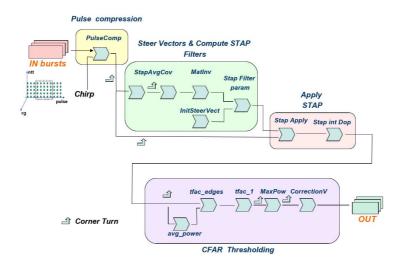

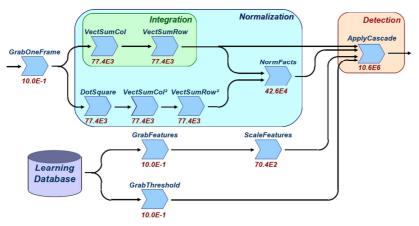

| FIGURE 3 STAP DATAFLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27            |

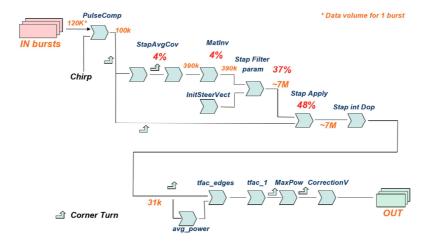

| FIGURE 4 STAP THROUGHPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28            |

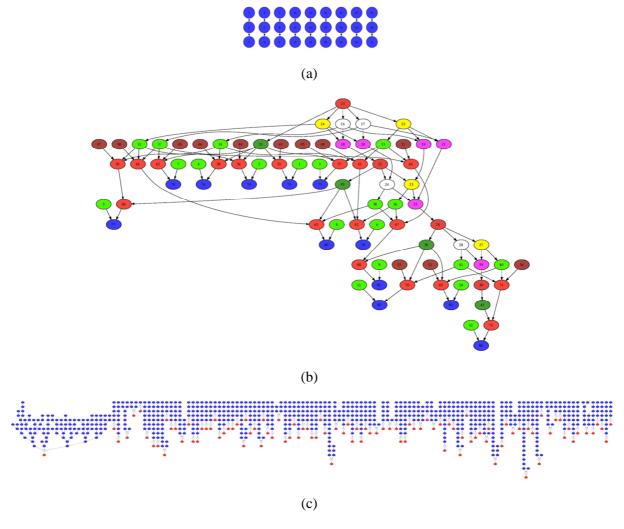

| FIGURE 5 VIOLA & JONES DATAFLOW AND THROUGHPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28            |

| Figure 6 Bandwidth requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30            |

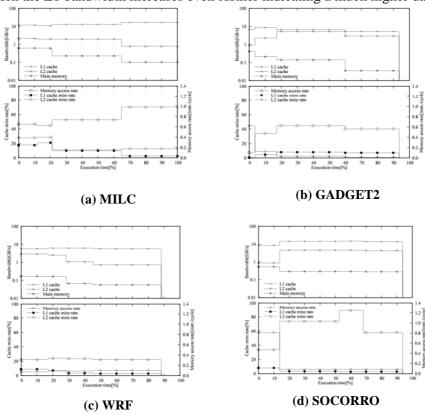

| FIGURE 7 MEMORY BANDWIDTH REQUIREMENTS OF SELECTED APPLICATIONS, AND THEIR ASSOCIATED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31            |

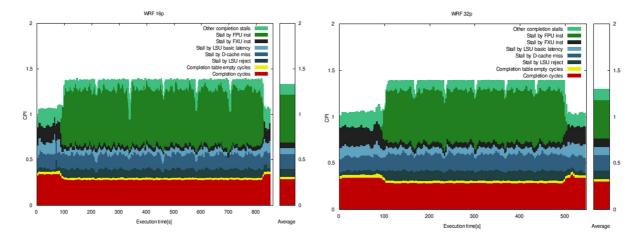

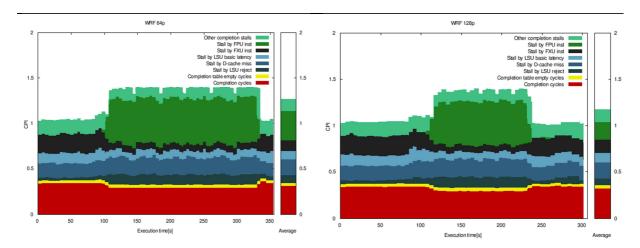

| FIGURE 8 CPI BREAKDOWN FOR WRF, RUNNING ON 16, 32, 64, 128 PROCESSORS. RESULTS ARE SHOWN FOR A STATE OF THE SHOWN FOR A S | SINGLE SAMPLE |

| THREAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33            |

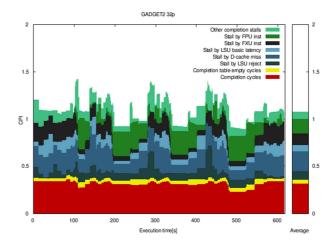

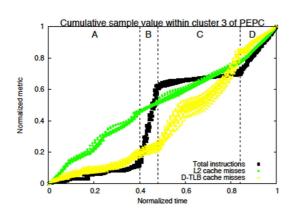

| FIGURE 9 CPI BREAKDOWN FOR GADGET2, RUNNING ON 32, 64, 128 PROCESSORS (THE DATASET IS TOO BIG TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FIT ON A 16   |

| PROCESSOR CONFIGURATION). RESULTS ARE SHOWN FOR A SINGLE SAMPLE THREAD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

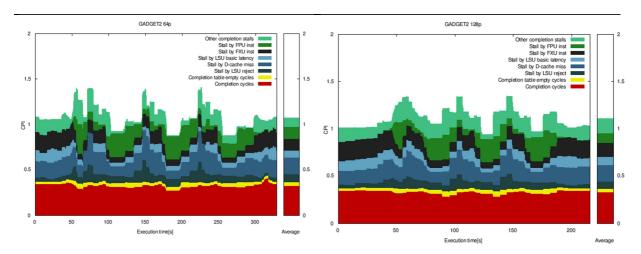

| FIGURE 10 IMPACT OF NETWORK IN GADGET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35            |

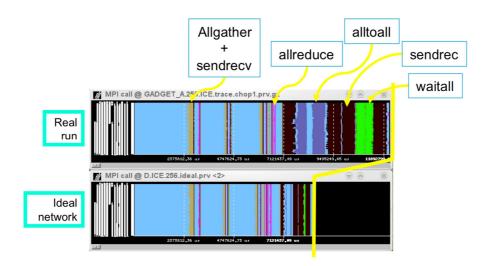

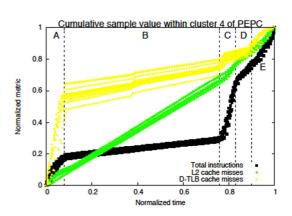

| FIGURE 11 IMPACT OF L2 CACHE MISSES AND D-TLB MISSES IN PERFORMANCE OF PEPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36            |

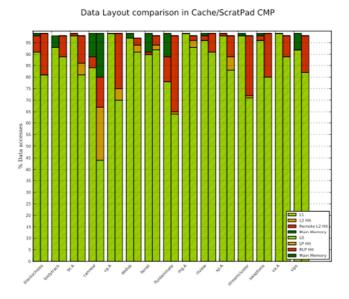

| FIGURE 12 DATA LAYOUT FOR PARSEC/NAS BENCHMARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37            |

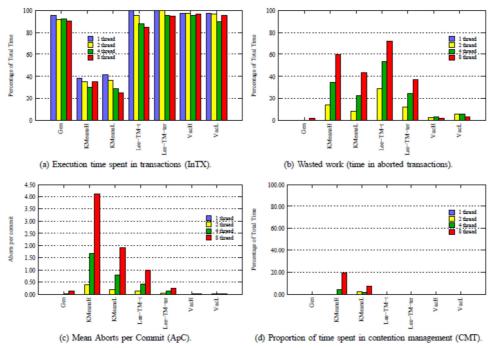

| FIGURE 13 TRANSACTIONAL MEMORY APPLICATION LEVEL METRICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39            |

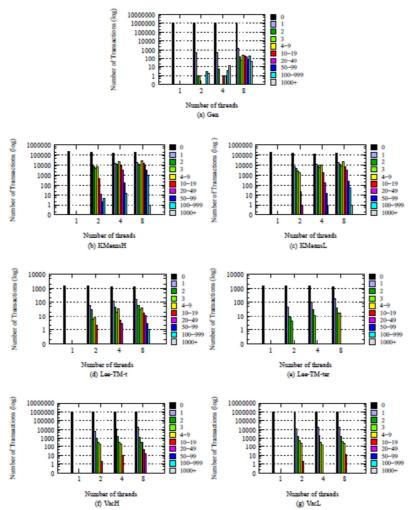

| Figure 14 Abort histograms for $TM$ benchmarks. Each bar represents the number of transactions $T$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HAT ABORTED A |

| GIVEN NUMBER OF TIMES BEFORE ACTUALLY COMMITTING. NOTE Y-AXIS USES LOGARITHMIC SCALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40            |

| FIGURE 15 TRANSACTION EXECUTION TIME HISTOGRAMS. THE COLOUR OF EACH BAR REPRESENTS A RANGE OF ELA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| TIMES IN MILLISECONDS. THE VERTICAL AXIS REPRESENTS THE NUMBER OF TRANSACTIONS COMPLETING WITH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| RANGE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

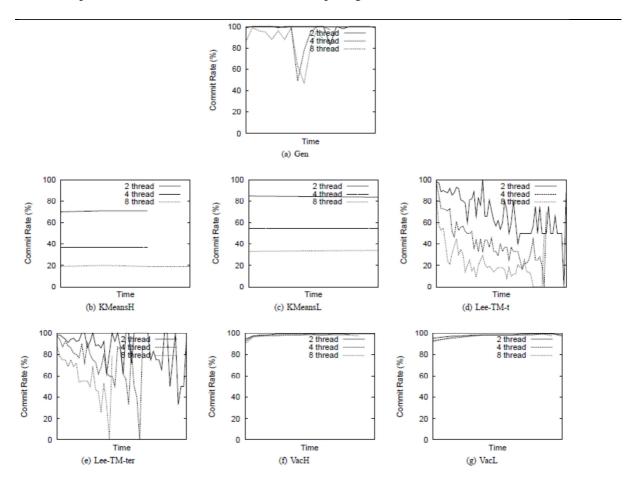

| FIGURE 16 INSTANTANEOUS COMMIT RATE (ICR) GRAPHS. IN OUR EXPERIMENTS WE SAMPLED AT 5 SECOND INTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| RATE FOR 2,4 AND 8 THREADS ARE PLOTTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| Table 1. List of Kernels and Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

| TABLE 2 LIST OF FULL APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| TABLE 3 LIST OF EXAMINED APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| TABLE A TRANSACTIONAL MEMORY BENCHMARKS LISED IN THE INITIAL CHARACTERIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30            |

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

The following list of authors will be updated to reflect the list of contributors to the writing of the document.

#### Rosa M. Badia, Yoav Etsion, Jesus Labarta, Nacho Navarro, Milan Pavlovic, Harald Servat, Carlos Villavieja BSC

#### **Sylvain Girbal**

Thales

## Mohammad Ansari, Mikel Lujan, Chris Kirkham, Ian Watson UNIMAN

#### Roberto Giorgi, Antoni Portero UNISI

#### Albert Cohen INRIA

#### © 2009 TERAFLUX Consortium, All Rights Reserved.

Document marked as PU (Public) is published in Italy, for the TERAFLUX Consortium, on the <a href="www.teraflux.eu">www.teraflux.eu</a> web site and can be distributed to the Public.

The list of author does not imply any claim of ownership on the Intellectual Properties described in this document.

The authors and the publishers make no expressed or implied warranty of any kind and assume no responsibilities for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information contained in this document.

This document is furnished under the terms of the TERAFLUX License Agreement (the "License") and may only be used or copied in accordance with the terms of the License. The information in this document is a work in progress, jointly developed by the members of TERAFLUX Consortium ("TERAFLUX") and is provided for informational use only.

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to TERAFLUX Partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of TERAFLUX is prohibited. This document contains material that is confidential to TERAFLUX and its members and licensors. Until publication, the user should assume that all materials contained and/or referenced in this document are confidential and proprietary unless otherwise indicated or apparent from the nature of such materials (for example, references to publicly available forms or documents).

Disclosure or use of this document or any material contained herein, other than as expressly

permitted, is prohibited without the prior written consent of TERAFLUX or such other party that may grant permission to use its proprietary material. The trademarks, logos, and service marks displayed in this document are the registered and unregistered trademarks of TERAFLUX, its members and its licensors. The copyright and trademarks owned by TERAFLUX, whether registered or unregistered, may not be used in connection with any product or service that is not owned, approved or distributed by TERAFLUX, and may not be used in any manner that is likely to cause customer confusion or that disparages TERAFLUX. Nothing contained in this document should be construed as granting by implication, estoppel, or otherwise, any license or right to use any copyright without the express written consent of TERAFLUX, its licensors or a third party owner of any such trademark.

Printed in Siena, Italy, Europe.

Part number: please refer to the File name in the document footer.

#### DISCLAIMER

EXCEPT AS OTHERWISE EXPRESSLY PROVIDED, THE TERAFLUX SPECIFICATION IS PROVIDED BY TERAFLUX TO MEMBERS "AS IS" WITHOUT WARRANTY OF ANY KIND, EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT OF THIRD PARTY RIGHTS.

TERAFLUX SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES OF ANY KIND OR NATURE WHATSOEVER (INCLUDING, WITHOUT LIMITATION, ANY DAMAGES ARISING FROM LOSS OF USE OR LOST BUSINESS, REVENUE, PROFITS, DATA OR GOODWILL) ARISING IN CONNECTION WITH ANY INFRINGEMENT CLAIMS BY THIRD PARTIES OR THE

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

SPECIFICATION, WHETHER IN AN ACTION IN CONTRACT, TORT, STRICT LIABILITY, NEGLIGENCE, OR ANY OTHER THEORY, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

## **Glossary**

BW Bandwidth

CPI Cycles per Instruction

DDM Data-Driven Multithreading

DTA Decoupled Threaded Architecture

HPC High Performance Computing

HPEC High Performance Embedded Computing

L Latency

StarSs Star Superscalar

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

## **Executive Summary**

This document is the first deliverable of WP2, Benchmarks and Applications. The objective of this workpackage is to understand the runtime behaviour of applications in order to establish a guideline in the design of the other components of the computing system in TERAFLUX. As TERAFLUX explores the design of highly parallel teradevice systems, a key step in the project is understanding the fundamental requirements of highly parallel applications and their implications on all layers of a computing system that supports a data-flow programming and execution model – from the programming model itself, down to extensions to commodity architecture.

The deliverable describes the results of the first year of the project in tasks 2.1 and task 2.2. While task 2.1 is finished, task 2.2 will continue during the second year of the project. The activities performed in task 2.1 relate to the selection of the applications and benchmarks to be used in the project. The criteria used to select the applications include aspects implicit to the application (domain, inherent parallelism, data-flow characteristics, transactional memory requirements) and others related to practical aspects (availability of the code, availability of realistic input data, previous experience of partners with the code...). The codes have been classified in two lists: kernels/benchmarks and full applications.

In order to make the kernels, benchmarks and applications available to all partners in a uniform distribution, a disk image is based on a Linux installation where all the necessary libraries and environments have been installed (i.e. MPI, StarSs runtime). The disk contains both the compiled codes with all the necessary data to be able to run them, and also the source code, scripts and Makefile to be able to rebuild them. The format was chosen such that it would natively plug into the COTSon simulation platform, and the partners can therefore configure the simulation platform to simply boot Linux from the disk image and run the applications.

The activities performed in task 2.2 relate to the characterization of the applications. The parameters that will be used to characterise the applications have been classified into resource requirements (memory bandwidth, network latency and bandwidth, parallelism,...) and TERAFLUX specific requirements (transactional memory and data flow). A description of the methodologies to be used is given in section 3. While some of them are based on analytical methods, a large bunch of them are based on tracefile generation of real runs and different types of post-processing and automatic analysis methods. Section 4 presents a description of initial results for some of the project applications.

Deliverable number: D2.1

Deliverable name: Report on the reference set of applications chosen, and initial

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

## 1 Introduction

This is the first deliverable of WP2, Benchmarks and Applications. Understanding the runtime behaviour of applications is a crucial guideline in the design of computing systems, as they are the effective consumers of the underlying compute power. As TERAFLUX explores the design of highly parallel teradevice systems, a key step in the project is understanding the fundamental requirements of highly parallel applications and their implications on all layers of a computing system that supports a data-flow programming and execution model – from the programming model themselves, down to extensions to commodity architecture. This exploration includes:

- Identify applications that can serve as reference applications for a programming model based on data-flow principles, and that can efficiently scale to utilize teradevice system.

- Characterize the resource requirements of these highly parallel applications, in terms of memory usage, bandwidth, and latency. Identify the performance requirements from underlying interconnection network. These characteristics will assist the architectural exploration performed in WP6.

- Uncover common data-flow and data-locality patterns implicit to the reference applications that can be disseminated into the programming model (WP3) as either data-flow or transactional semantics.

- Port a few applications to the programming models chosen by WP3. Initially, we will

consider the StarSs (BSC) and DDM (UCY) programming model, and the DTA (UNISI)

execution models. The ported applications will be used by the other work packages to guide

their proposed designs.

- Extract the interesting patterns and data accesses and that will assist other work packages build sensible benchmarks that can test the proposed constructs in all domains: programming model (WP3), compilation platform (WP4), reliability (WP5) and architecture (WP6).

#### 1.1 Document structure

The deliverable is organized as follows: this section introduces the deliverable and its structure, section 2 describes the criteria that have been used to select the applications and benchmarks and lists the actual selected ones (task 2.1). Section 3 presents the parameters that will be the object of the applications' characterization and explains the methodologies that will be used in this characterization. Section 4 presents some initial results of the characterization and finally section 5 concludes the document.

#### 1.2 Relation to other deliverables

No specific one.

## 1.3 Activities referred by this deliverable

This deliverable refers to the activities performed in tasks 2.1 and 2.2 during the first year of the project. Task 2.2 will continue its activities during the second year of the project.

Deliverable number: D2.1