Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

# SEVENTH FRAMEWORK PROGRAMME THEME

FET proactive 1: Concurrent Tera-Device Computing (ICT-2009.8.1)

**PROJECT NUMBER: 249013**

## **Exploiting dataflow parallelism in Teradevice Computing**

## D7.4 – Report on knowledge transfer and training

Due date of deliverable: 31<sup>st</sup> December 2012 Actual Submission: 20<sup>th</sup> December 2012

Start date of the project: January 1<sup>st</sup>, 2010 Duration: 48 months

# Lead contractor for the deliverable: UNISI

**Revision**: See file name in document footer.

| Project co-founded by the European Commission within the SEVENTH FRAMEWORK PROGRAMME (2007-2013) |                                                                                       |  |  |  |  |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Disser                                                                                           | Dissemination Level: PU                                                               |  |  |  |  |

| PU                                                                                               | Public                                                                                |  |  |  |  |

| PP                                                                                               | Restricted to other programs participant (including the Commission Services)          |  |  |  |  |

| RE                                                                                               | Restricted to a group specified by the consortium (including the Commission Services) |  |  |  |  |

| CO                                                                                               | Confidential, only for members of the consortium (including the Commission Services)  |  |  |  |  |

#### **Change Control**

| Version# | Author         | Organization | Change History                     |

|----------|----------------|--------------|------------------------------------|

| 0.1      | Marco Solinas  | UNISI        | Initial template                   |

| 1.0      | Marco Solinas  | UNISI        | UNISI parts                        |

| 1.2      | Marco Solinas  | UNISI        | Added contributions from partners  |

| 2.1      | Roberto Giorgi | UNISI        | Final revision                     |

| 3.0      | Marco Solinas  | UNISI        | Executive Summary and Introduction |

#### **Release Approval**

| Name           | Role        | Date       |

|----------------|-------------|------------|

| Marco Solinas  | Originator  | 08.11.2012 |

| Roberto Giorgi | WP Leader   | 28.11.2012 |

| Roberto Giorgi | Coordinator | 13.12.2012 |

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 1 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

# **TABLE OF CONTENT**

| G | GLOSSARY                                                                       | 4  |

|---|--------------------------------------------------------------------------------|----|

| E | EXECUTIVE SUMMARY                                                              | 7  |

| 1 | INTRODUCTION                                                                   | 8  |

|   | 1.1 RELATION TO OTHER DELIVERABLES                                             | 8  |

|   | 1.2 ACTIVITIES REFERRED BY THIS DELIVERABLE                                    | 9  |

|   | 1.3 SUMMARY OF PREVIOUS WORK (FROM D7.1, D7.2 AND D7.3)                        | 9  |

| 2 | NEW SIMULATION FEATURES                                                        | 10 |

|   | 2.1 Brief Overview of the TERAFLUX Evaluation Platform (ALL WP7 PARTNERS)      | 10 |

|   | 2.2 T* Instruction and Built-In Support in the C Language (UNISI, HP)          | 11 |

|   | 2.2.1 Brief Introduction to COTSon's Implementation of T*                      |    |

|   | 2.3 NEW T* BENCHMARKS (UNISI)                                                  | 16 |

|   | 2.3.1 Matrix Multiplier                                                        | 16 |

|   | 2.3.2 Other Benchmarks                                                         | 16 |

|   | 2.4 SINGLE NODE T* TESTS (UNISI)                                               | 17 |

|   | 2.4.1 T* Timing Model                                                          | 18 |

|   | 2.5 MULTI-NODE T* TESTS (UNISI)                                                | 19 |

|   | 2.5.1 Framework design                                                         | 20 |

|   | 2.5.2 Demonstration of multi-node capability of the new distributed scheduler  | 21 |

|   | 2.6 POWER ESTIMATION USING MCPAT (UNISI)                                       | 21 |

|   | 2.6.1 Off-line vs. on-line Power estimation                                    | 22 |

|   | 2.7 EXECUTION OF USER LEVEL DDM ON COTSON (UCY)                                | 24 |

|   | 2.8 INTEGRATING DDM TSU INTO COTSON (UCY)                                      | 25 |

|   | 2.9 GCC BACKEND AND OPENSTREAM EXPERIMENTS ON COTSON (INRIA)                   |    |

|   | 2.10 Double Execution and Thread Restart Recovery in a Single Node (COTSon Mod |    |

|   | (UAU, HP)                                                                      |    |

|   | 2.10.1 FDU subsystem in COTSon                                                 |    |

|   | 2.10.2 Double execution and Recovery Support                                   |    |

|   | 2.11 HIGH LEVEL FAULT INJECTION TECHNIQUE (COTSON MODULES) (UAU)               |    |

|   | 2.12 TRANSACTIONAL MEMORY SUPPORT IN COTSON (UNIMAN)                           |    |

|   | 2.12.1 Functional Transaction Support                                          |    |

|   | 2.12.2 Adding timing support with COTSon                                       |    |

| 3 |                                                                                |    |

|   | 3.1 THE "TFX3"- TERAFLUX SIMULATION HOST                                       |    |

|   | 3.2 PIKE – AUTOMATIZING LARGE SIMULATIONS (UNISI)                              |    |

|   | 3.2.1 Overall organization                                                     |    |

|   | 3.2.2 Functions Exposed to the User                                            |    |

|   | 3.2.3 Current limits                                                           |    |

|   | 3.2.4 Examples                                                                 |    |

|   | 3.3 THE ECLIPSE MODULE FOR TFLUX (UCY)                                         |    |

|   | 3.3.1 The Content Assistant Plug-in                                            |    |

|   | 3.3.2 The Side Panel Plug-in                                                   |    |

|   | 3.4 SUPPORT TO THE PARTNERS FOR IMPLEMENTING COTSON EXTENSIONS (HP)            | 43 |

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 2 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

| 3.5    | 1 UTORIAL SESSIONS ON OMPSS OPEN TO THE PARTNERS (BSC) |

|--------|--------------------------------------------------------|

| APPENI | DIX A45                                                |

|        |                                                        |

# LIST OF FIGURES

| FIG. 1 TERAFLUX EVALUATION PLATFORM                                                                         | 10        |

|-------------------------------------------------------------------------------------------------------------|-----------|

| FIG. 2 FIBONACCI(35): NUMBER OF THREADS IN FOUR SINGLE-NODE CONFIGURATIONS                                  | 17        |

| FIG. 3 FIBONACCI(35): NUMBER OF THREADS (ZOOMED DETAIL OF THE PREVIOUS FIGURE)                              | 18        |

| FIG. 4 TIMING MODEL FOR THE T* EXECUTION                                                                    | 19        |

| FIG. 5 THE STRUCTURE OF THE FRAMEWORK FOR MULTI-NODE SIMULATION AS IT IS RUNNING ON OUR SIMULATION HOST     | 20        |

| FIG. 6 MULTI-NODE SIMULATION: FIBONACCI, WITH INPUT SET TO 40, AND MATRIX MULTIPLY, WITH MATRIX SIZE 512X5. | 12,       |

| PARTITIONED IN A NUMBER OF BLOCKS EQUAL TO THE NUMBER OF CORES                                              | 21        |

| FIG. 7 POWER ESTIMATION SAMPLE OUTPUTS.                                                                     | 23        |

| FIG. 8 RUNNING DDM ON COTSON, WITH FOUR NODES                                                               | 24        |

| FIG. 9 BLOCKED MATRIX MULTIPLY RUNNING ON A FOUR CPU MACHINE                                                | 25        |

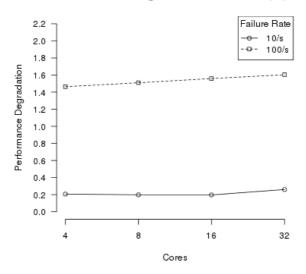

| FIG. 10 PERFORMANCE DEGRADATION OF FIBONACCI(40) USING THREAD FAILURE INJECTION WITH FAILURE RATES PER COR  | E OF 10/S |

| AND 100/s                                                                                                   | 29        |

| FIG. 11 EXTERIOR VISION OF THE DL-PROLIANT DL585, MAIN TERAFLUX SIMULATION SERVER                           | 32        |

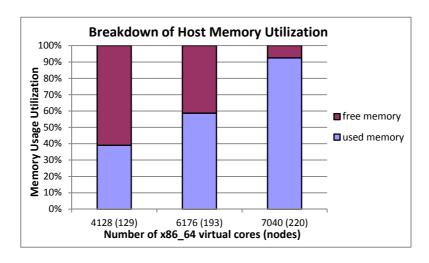

| Fig. 12 Host versus Virtual System                                                                          | 33        |

| Fig. 13 Number of Virtual Cores vs Memory utilization in HP ProLiant DL585 G7 Server (1 TB Memory, 64       | x86_64    |

| CORES)                                                                                                      | 33        |

| FIG. 14 EXECUTING PIKE IN SILENT MODE                                                                       | 34        |

| FIG. 15 EXECUTING PIKE IN VERBOSE MODE                                                                      | 35        |

| FIG. 16 SIMNOW INSTANCE WITH TEST EXAMPLE — SINGLE SIMULATION                                               | 37        |

| FIG. 17 TWO SIMNOW WINDOWS IN CASE OF MULTIPLE SIMULATION PIKE RUN                                          | 38        |

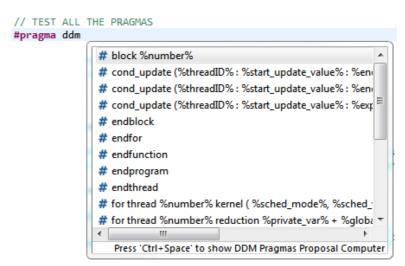

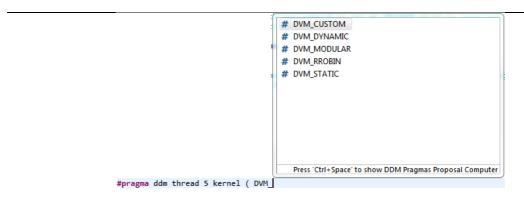

| FIG. 18: THE CONTENT ASSISTANT PLUG-IN LISTING THE AVAILABLE DDM KEYWORDS                                   | 39        |

| FIG. 19: THE CONTENT ASSISTANT PLUG-IN FILTERING THE DDM KEYWORDS STARTING WITH "DVM_" FOR THE SCHEDULIN    | IG POLICY |

| FIELD OF THE THREAD PRAGMA                                                                                  | 40        |

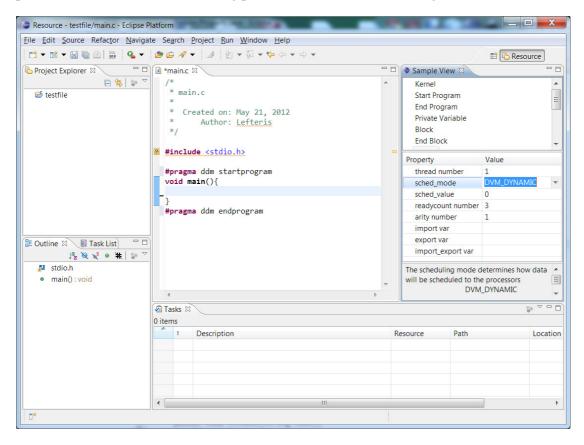

| FIG. 20: THE SIDE PANEL PLUG-IN IMPORTED TO THE ECLIPSE PLATFORM                                            | 40        |

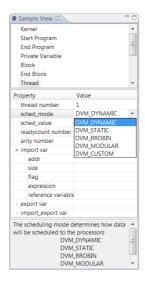

| FIG. 21: THE SIDE PANEL PLUG-IN SHOWING A DROP-DOWN LIST FOR THE OPTIONS OF THE SCHEDULING MODE             | 41        |

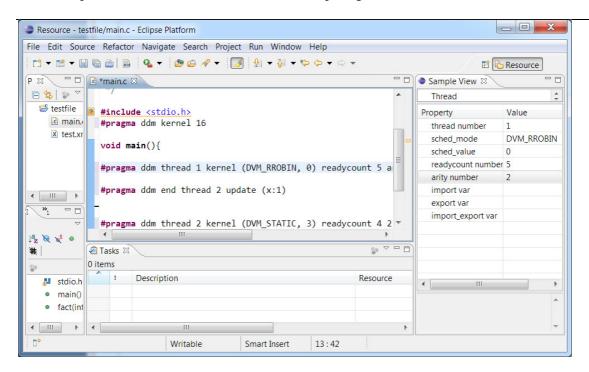

| FIG. 22: THE SIDE PANEL PLUG-IN AUTOMATICALLY CLOSING THE DDM PRAGMAS                                       |           |

| FIG. 23: THE SIDE PANEL PLUG-IN SHOWING THE PROPERTIES OF A SELECTED PRAGMA                                 | 42        |

| FIG. 24 DATAFLOW GRAPH FOR THE BLOCKED MATRIX MULTIPLICATION ALGORITHM.                                     | 45        |

Deliverable number: D7.4

Deliverable name: Report on knowledge transfer and training

File name: TERAFLUX-D74-v10.doc Page 3 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

# Glossary

| Giossai y           |                                                                            |

|---------------------|----------------------------------------------------------------------------|

| Auxiliary Core      | A core typically used to help the computation (any other core than service |

|                     | cores) also referred as "TERAFLUX core"                                    |

| BSD                 | BroadSword Document - In this context, a file that contains the SimNow     |

|                     | machine description for a given Virtual Machine                            |

| CDG                 | Codelet Graph                                                              |

| CLUSTER             | Group of cores (synonymous of NODE)                                        |

| Codelet             | Set of instructions                                                        |

| COTSon              | Software framework provided under the MIT license by HP-Labs               |

| DDM                 | Data-Driven Multithreading                                                 |

| DF-Thread           | A TERAFLUX Data-Flow Thread                                                |

| DF-Frame            | the Frame memory associated to a Data-Flow thread                          |

| DVFS                | Dynamic Voltage and Frequency Scaling                                      |

| DTA                 | Decoupled Threaded Architecture                                            |

| DTS                 | Distributed Thread Scheduler                                               |

| Emulator            | Tool capable of reproducing the functional behavior; synonymous in this    |

|                     | context of Instruction Set Simulator (ISS)                                 |

| D-FDU               | Distributed Fault Detection Unit                                           |

| ISA                 | Instruction Set (Architecture)                                             |

| ISE                 | Instruction Set Extension                                                  |

| L-Thread            | Legacy Thread: a thread consisting of legacy code                          |

| L-FDU               | Local Fault Detection Unit                                                 |

| L-TSU               | Local Thread Scheduling Unit                                               |

| MMS                 | Memory Model Support                                                       |

| NoC                 | Network on Chip                                                            |

| Non-DF-Thread       | An L-Thread or S-Thread                                                    |

| NODE                | Group of cores (synonymous of CLUSTER)                                     |

| OWM                 | Owner Writeable Memory                                                     |

| OS                  | Operating System                                                           |

| Per-Node-Manager    | A hardware unit including the DTS and the FDU                              |

| PK                  | Pico Kernel                                                                |

| Sharable-Memory     | Memory that respects the FM, OWM, TM semantics of the TERAFLUX             |

|                     | Memory Model                                                               |

| S-Thread            | System Thread: a thread dealing with OS services or I/O                    |

| StarSs              | A programming model introduced by Barcelona Supercomputing Center          |

| <b>Service Core</b> | A core typically used for running the OS, or services, or dedicated I/O or |

|                     | legacy code                                                                |

| Simulator           | Emulator that includes timing information; synonymous in this context of   |

|                     | "Timing Simulator"                                                         |

| TAAL                | TERAFLUX Architecture Abstraction Layer                                    |

| TBM                 | TERAFLUX Baseline Machine                                                  |

| TLPS                | Thread-Level-Parallelism Support                                           |

| TLS                 | Thread Local Storage                                                       |

|                     |                                                                            |

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 4 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

| TM                               | Transactional Memory        |

|----------------------------------|-----------------------------|

| TMS Transactional Memory Support |                             |

| TP                               | Threaded Procedure          |

| Virtualizer                      | Synonymous with "Emulator"  |

| VCPU                             | Virtual CPU or Virtual Core |

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 5 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

The following list of authors will be updated to reflect the list of contributors to the writing of the document.

# Marco Solinas, Alberto Scionti, Andrea Mondelli, Ho Nam, Antonio Portero, Stamatis Kavvadias, Monica Bianchini, Roberto Giorgi

Università di Siena

#### Arne Garbade, Sebastian Weis, Theo Ungerer

Universitaet Augsburg

Antoniu Pop, Feng Li, Albert Cohen INRIA

# Lefteris Eleftheriades, Natalie Masrujeh, George Michael, Lambros Petrou, Andreas Diavastos, Pedro Trancoso, Skevos Evripidou

University of Cyprus

#### Nacho Navarro, Rosa Badia, Mateo Valero

Barcelona Supercomputing Center

#### Paolo Faraboschi

Hewlett Packard Española

#### Behram Khan, Salman Khan, Mikel Lujan, Ian Watson

The University of Manchester

2009-13 TERAFLUX Consortium, All Rights Reserved.

Document marked as PU (Public) is published in Italy, for the TERAFLUX Consortium, on the www.teraflux.eu web site and can be distributed to the Public.

The list of author does not imply any claim of ownership on the Intellectual Properties described in this document. The authors and the publishers make no expressed or implied warranty of any kind and assume no responsibilities for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information contained in this document. This document is furnished under the terms of the TERAFLUX License Agreement (the "License") and may only be used or copied in accordance with the terms of the License. The information in this document is a work in progress, jointly developed by the members of TERAFLUX Consortium ("TERAFLUX") and is provided for informational use only.

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to TERAFLUX Partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of TERAFLUX is prohibited. This document contains material that is confidential to TERAFLUX and its members and licensors. Until publication, the user should assume that all materials contained and/or referenced in this document are confidential and proprietary unless otherwise indicated or apparent from the nature of such materials (for example, references to publicly available forms or documents).

Disclosure or use of this document or any material contained herein, other than as expressly permitted, is prohibited without the prior written consent of TERAFLUX or such other party that may grant permission to use its proprietary material. The trademarks, logos, and service marks displayed in this document are the registered and unregistered trademarks of TERAFLUX, its members and its licensors. The copyright and trademarks owned by TERAFLUX, whether registered or unregistered, may not be used in connection with any product or service that is not owned, approved or distributed by TERAFLUX, and may not be used in any manner that is likely to cause customer confusion or that disparages TERAFLUX. Nothing contained in this document should be construed as granting by implication, estoppel, or otherwise, any license or right to use any copyright without the express written consent of TERAFLUX, its licensors or a third party owner of any such trademark.

Printed in Siena, Italy, Europe.

Part number: please refer to the File name in the document footer.

#### DISCLAIMER

EXCEPT AS OTHERWISE EXPRESSLY PROVIDED, THE TERAFLUX SPECIFICATION IS PROVIDED BY TERAFLUX TO MEMBERS "AS IS" WITHOUT WARRANTY OF ANY KIND, EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT OF THIRD PARTY RIGHTS.

TERAFLUX SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES OF ANY KIND OR NATURE WHATSOEVER (INCLUDING, WITHOUT LIMITATION, ANY DAMAGES ARISING FROM LOSS OF USE OR LOST BUSINESS, REVENUE, PROFITS, DATA OR GOODWILL) ARISING IN CONNECTION WITH ANY INFRINGEMENT CLAIMS BY THIRD PARTIES OR THE SPECIFICATION, WHETHER IN AN ACTION IN CONTRACT, TORT, STRICT LIABILITY, NEGLIGENCE, OR ANY OTHER THEORY, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Deliverable number: D7.4

Deliverable name: Report on knowledge transfer and training

File name: TERAFLUX-D74-v10.doc Page 6 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

# **Executive Summary**

In this report, we provide a description of the integration activity, through the COTSon simulation platform, of the research of the TERAFLUX partners, as progressed during the third year of the project. Thanks to the common simulator tools and internal dissemination, partners have been also able to transfer their respective research knowledge to the other partners.

The support for T\* instructions has been implemented in the simulator: this means that partners are now able to run actual benchmarks containing the DATAFLOW Instruction Set Extension (T\* ISE) designed in the previous period of the project. The Thread Scheduling Unit provides full support for the execution of TSCHEDULE, TDESTROY, TREAD and TWRITE (variants of these basic instructions are also implemented in the simulator, in order to meet some compiler needs highlighted by the partners working on WP4). An interface for injecting directly such T\* built-ins in C applications is also available, and in this report we provide the description of some first kernel benchmarks (i.e., the Recursive Fibonacci and Matrix Multiply) exploiting this feature. The support of the GCC compiler for generating executable T\* binaries directly from OpenStream annotated C code is also available to partners, and applications ready-to-compile are also published in the public repository. Finally, the support for multimode Transactional Memory is implemented in the simulator, and available to all the Partners and publicly available for download and run. We believe that all the above will enhance the capability of the research community to simulate Teradevice systems.

The multi-node Distributed Thread Scheduler (DTS – a key element of the TERAFLUX Architecture) has been also implemented in COTSon, and is also publicly available for downloading and running experiments. In this report, we show how the very same T\* application-binaries running on the single-node configuration have been also successfully run in a multi-node system. This implementation of the multi-node DTS currently encompasses the functional implementation and a partial timing model (not fully connected with other component timing models). The support for power estimation is now integrated in the evaluation platform. The Fault Detection Unit (FDU) subsystem is also implemented in COTSon, providing support for double execution of threads, and thread restart/recovery, both in the single-node case. Moreover, in order to test the correctness and effectiveness of the fault detection mechanisms, the single-node DTS implementation has been extended with a high level fault injection technique, which is also described in this deliverable. Moreover, other Dataflow variants, like the Data-Driven Multithreading (DDM) - from the UCY Partner, have been also tested in COTSon, both in the single-node and multi-node configurations.

All the newly implemented characteristics have been successfully integrated in the common platform also thanks to the support provided by the HP partner (which released COTSon at the very beginning of this project) to all the TERAFLUX partners.

A new tool (called PIKE) for extending the knowledge details to perform "large target-machine" simulations has been realized and released in the public repository, to the TERAFLUX partners and, more in general, to the scientific community. This tool acts as a wrapper of the COTSon simulator, and simplifies the configuration process needed for running a set of simulations, thus speeding-up the evaluation process of newly-implemented research solution.

The originally planned simulation server is available to all the TERAFLUX partners.

Finally, tutorial sessions on OmpSS have been organized by BSC; such tutorials were open to all the TERAFLUX partners.

Deliverable number: D7.4

Deliverable name: Report on knowledge transfer and training

File name: TERAFLUX-D74-v10.doc Page 7 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

#### 1 Introduction

The main objective of the workpackage WP7 is to drive the integration of the research performed by each TERAFLUX partner. This is done mainly by means of a common simulation infrastructure, the COTSon simulator, which can be modified by partners in order to meet their research needs while transferring the reciprocal knowledge to the other partners. In this report, we provide a summary of the activities performed by the TERAFLUX Consortium during the third year of the project, working on the common evaluation platform (see section 2.1 for an introduction to this concept).

As the content of this Deliverable shows, the knowledge transfer about the simulation infrastructure to the TERAFLUX Partners has been very successful.

The T\* instructions have been introduced as an extension of the x86\_64 ISA, as designed in D7.2, and are now integrated in the simulator: we provide a high-level description of the fundamental mechanisms in section 2.2. Since an interface for writing C applications has also been realized, we report in section 2.4 a brief description of some kernel benchmarks that we realized, while the compiler support for generating T\* applications is reported in section 2.9. The extension of the TSU to the multi-node case is now available to partners, as described in section 2.5; in section 2.4 we describe the first steps of the implementation of a timing model for T\* instructions, in the single-node case, which is still an ongoing activity. The available mechanism for estimating power consumption is reported in section 2.6.

In section 2.7 and 2.8, the activities performed for integrating in COTSon the DDM-style hardware scheduler are reported. The implementation of the FDU mechanisms for double execution and thread restart-recovery are described in section 2.10, while section 2.11 provides a description of the fault injection model. The enhanced support for Transactional Memory (for the multi-node case) to COTSon is discussed in section 2.12.

Finally, in section 3 we describe the simulation environment and the support that was made available to the Partners, from both the hardware side and software side. Moreover, in section 3.5 we report on some training events on OmpSS, organized by BSC and opened to TERAFLUX partners.

#### 1.1 Relation to Other Deliverables

The activities under the WP7 are related to the integration of the research performed in the other TERAFLUX workpackages. In particular, we highlight the following relations:

- M7.1 (WP7): for the first architectural definition;

- D2.1, D2.2 (WP2): for the definition of the TERAFLUX relevant set of applications;

- D4.1, D4.3 (WP4): for the compilation tools towards T\*;

- D5.1, D5.2, D5.3 for FDU details;

- D6.1, D6.2, D6.3 (WP6): architectural choices taken during the first 3 years of the project;

- D7.1, D7.2, D7.3 (WP7): previous research under this WP.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 8 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

### 1.2 Activities Referred by this Deliverable

This deliverable reports on the research carried out in the context of Task 7.1 (m1-m48) and Task 7.3 (m6-m40). In particular, Task 7.1 covers an ongoing activity for the entire duration of the project that ensures the tools are appropriately disseminated and supported within the consortium (see Annex 1, page 52), while Task 7.3 is related to the implementation in the common evaluation platform of the fault injection and power models (see Annex 1, page 53).

#### 1.3 Summary of Previous Work (from D7.1, D7.2 and D7.3)

During the first two years, the TERAFLUX partners started using COTSon, and modified it in order to implement (test and validate) new features, to meet their research needs. In particular, we are able to boot a 1000+ cores machine, based on the baseline architectural template described in D7.1. The target architecture can exploit all the features added by the various partners to the common platform: this is very important for the integration of the research efforts carried out in the various TERAFLUX WPs. In particular, an initial FDU interface with the TSU (both DTS style and DDM style), has been described in D7.2, and further detailed in D7.3. Similarly, in D7.3 a first model for the development to monitor power consumption and temperature was reported.

Deliverable number: D7.4

Deliverable name: Report on knowledge transfer and training

File name: TERAFLUX-D74-v10.doc Page 9 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

#### 2 New Simulation Features

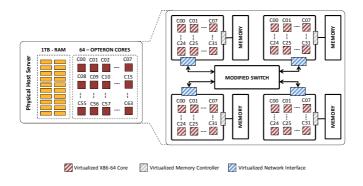

# 2.1 Brief Overview of the TERAFLUX Evaluation Platform (ALL WP7 PARTNERS)

The TERAFLUX project relies on a common evaluation platform that is used by the partners with two purposes: *i*) evaluate and share their research by using such integrated, common platform, and *ii*) transfer to the other partners the reciprocal knowledge of such platform.

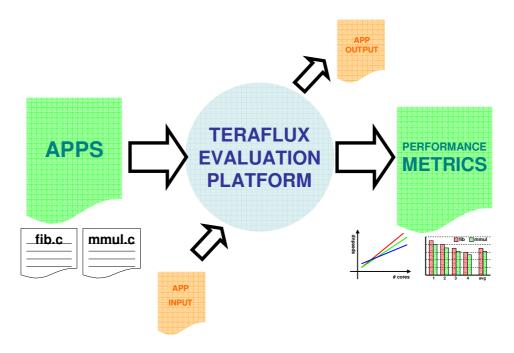

In Fig. 1 is shown the high-level vision of the evaluation platform.

Fig. 1 TERAFLUX evaluation platform.

The *APPS* block represents the applications that researches can feed to the evaluation platform, as well as other "pipe-cleaner" benchmarks like the ones described in Section 2.3 of this document, or the ones coming from the activities of WP2. Another important point emerged by the WP2, is a proper choice of the inputs, in order to be able to show the performance at the "TERADEVICE level" (i.e., for at least 1000 complex cores, as discussed in previous deliverables like D7.1, D7.2, D7.3, i.e., 1000 x  $10^9$  transistor devices).

The TERAFLUX evaluation platform is the set of common tools available to partners: the extended simulator (i.e., the extended COTSon, see sections 2.2, 2.4, 2.8, 2.10, and 2.11), compilers (see section 2.9), the hardware for hosting simulations (see section 3.1), and external tools for power estimation (see section 2.6), or to easily configure and run the simulator (see section 3.2). The *output* block represents the outcome of the benchmarks, while the *performance metrics* are the set of statistics that can be obtained when executing benchmarks in the common platform (see sections 2.4 and 2.5). Finally, in this context, the *app output* is necessary for verifying the application had executed correctly during the evaluation.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 10 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

#### 2.2 T\* Instruction and Built-In Support in the C Language (UNISI, HP)

In the TERAFLUX project, the T\* Instruction Set Extensions (ISE) to the x86\_64 ISA has been introduced for managing threads in a dataflow style by means of dedicated hardware units for executing the custom instructions. In order to experiment with these T\* new instructions, we used a simulation mechanism which overloads a set of unused existing x86 instructions, thus allowing us to rely on very well tested virtualizer like SimNOW (part of COTSon).

In order to simulate this feature in COTSon and have more flexibility in the register mapping of the compiler, we overload the semantic of a particular x86\_64 instruction, called prefetchnta. This has the advantage of being a "hint" with no architecturally visible side-effect and does not clobber any architectural register. From the x86\_64 instruction manual [x86]:

#### prefetchnta m8

where **m8** is a byte memory address respecting the x86\_64 indexed base + offset format ([x86], Chapter 2). This instruction is harmless to the core execution, since it is just a "cache hint": that's why we selected it as the mechanism to convey "additional information" into the simulator. It is also rich enough to support a large encoding space, as well as immediates and registers for T\* instructions, as we describe in more details below. The "additional information" include the T\* opcodes and its parameters, as introduced in D6.1, D6.2, as well as other T\* new instructions, besides the 6 original ones introduced in D7.1, D6.2, whose need became clearer as we started experimenting with more complex code. Moreover, this instruction is a good match to the compilation tools because it doesn't alter any content of the general purpose registers. For example, other user-defined functionalities of COTSon, and the initial T\* implementation, use CPUID (see D7.1, D7.2), which has the unpleasant side effect of modifying RAX, RBX, RCX, RDX, which causes compiler complexity and unnecessary spill/restore overhead.

In order to minimize the probability of overloading an instruction used in regular code, we selected as MOD R/M byte [x86] the value 0x84, which means that m8 specifies a (32-bit) memory address that is calculated as [%base]+[%index]\*2<sup>scale</sup>+displacement32. The %base, %index register identifiers and the scale bits (2 bits), are packed in a so-called SIB byte [x86]. displacement32 is another 4 bytes. In such case, we have a total of 5 bytes (after the opcode and the MOD R/M byte) that are available for the encoding of T\* ISE. We then defined a "magic value" (0x2daf), as a reserved prefix that indicates a prefetch of 0x2daf0000 (766,443,520 bytes) of a scaled index and base address, which is not something that has any conceivable use in practice. As a matter of fact, we tested routine execution of a running system for several billion instructions, as well as all the binaries shipped with our standard Linux distribution, without any occurrence of that instruction. With the above choices, the overloaded instruction encoding looks as follows:

where 0x0F18 is the x86 opcode for prefetchnta, 0x84 is the value of the MOD R/M field of the prefetchnta instruction, 'rr' (1 byte, that was corresponding the SIB byte), 'II' (1 byte) and 'XX' (1byte) are the two remaining byte from the displacement.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 11 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

This allows us to use:

• The **rr** value for encoding two x86 registers is used in the T\* instruction. We currently chose to limit the registers to the core set available in both 32b and 64b x86 ISA variants for simplicity, but we may extend the choice to more 64b registers in the future if the need for additional registers arises

- The **XX** value for encoding the T\* opcode (for up to 256 opcodes)

- The **II** value for encoding an 8-bit T\* immediate, if needed (or other 2 registers like for the **rr** field).

Let's consider, as an example, what happens with a **TREAD** operation (see D6.2 Table 1) from the frame memory of a DF-thread, at the "slot" number 5. The compiler should then target such T\* built-in. For testing, we also provide a set of C-language built-ins that can be embedded in manual C code, and would be expressed **DF\_TREAD(5)** as shown here (a more extensive example is provided in Appendix A for quick reference):

```

uint64_t a;

a = DF_TREAD(5);

```

This will then be assembled as:

```

prefetchnta 0x2daf050e(%rdx,%rdx,1)

```

and will have a meaning:

```

TREAD $5, %rdx.

```

In fact, the corresponding bytes representing the instruction will be:

```

OF 18 84 12 OE 05 AF 2D

```

The "container" of the custom instruction is therefore **0x0F1884...AF2D**, which is already described above and is the same for all the custom instructions. The "useful bits" (underlined) are:

- 0x12 specifies the identifier of the destination register of the TREADQI (which is connected to the destination variable 'a' by the gcc-macro expansion),

- **0x0E** is the T\* opcode for TREADQI (TREAD with immediate value other currently experimented opcodes are reported below),

- **0x05**, this is the immediate value of the DF\_TREAD.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 12 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

In Table 1, we provide the full list of all the  $T^*$  ISE opcode (i.e., all the possible values for the **XX** field) introduced so far in the COTSon simulator.

Table 1 OPCODEs for T\* instructions (the instructions with the grey background in this table have been reported for completeness, but have not yet been fully implmented in the simulator)

| OPCODE | INSTRUCTION | OPCODE | INSTRUCTION  | OPCODE | INSTRUCTION |

|--------|-------------|--------|--------------|--------|-------------|

| 0x01   | TINIT       | 0x0D   | TSCHEDULEI   | 0x19   | TDECREASEN  |

| 0x02   | TSCHEDULE   | 0x0E   | TREADQI      | 0x1A   | TDECREASENI |

| 0x03   | TREAD       | 0x0F   | TWRITEQI     | 0x1B   | TWRITEP     |

| 0x04   | TWRITE      | 0x10   | TSCHEDULEP   | 0x1C   | TWRITEPI    |

| 0x05   | TALLOC      | 0x11   | TESCHEDULEPI | 0x1D   | TWRITEQPI   |

| 0x06   | TFREE       | 0x12   | TLOAD        | 0x1E   | TSCHEDULEZ  |

| 0x07   | TPOLL       | 0x13   | TSTORE       | 0x1F   | TWRITE32P   |

| 0x08   | TRESET      | 0x14   | TSTOREQI     | 0x20   | TWRITE32PI  |

| 0x09   | TSTAMP      | 0x15   | TSCHEDULEF   | 0x21   | TSTOREP     |

| 0x0A   | TDESTROY    | 0x16   | TSCHEDULEFI  | 0x22   | TSTOREPI    |

| 0x0B   | TREADI      | 0x17   | TCACHE       |        |             |

| 0x0C   | TWRITEI     | 0x18   | TDECREASE    |        |             |

## 2.2.1 Brief Introduction to COTSon's Implementation of T\*

The set of supported T\* ISE, currently experimented, is the following.

- **tschedulepi** % **tid** = % **ip**, % **cnd**, \$sc: Schedules (conditionally) a thread with address in register % ip to be executed. Register % cnd holds the predicate. The immediate \$sc holds the synchronization count (0..255). It returns a thread handle in register % tid, or 0 if the predicate is false<sup>1</sup>. The % tid is guaranteed to have bits 0..31 at 0 (see **TWRITE**). Constraint: % tid and % ip must specify the same register identifier (i.e., the same x86\_64 register). For variable sc or sc > 255, the general version (**TSCHEDULEP**) is required.

- **tdestroy** %**dfr**: Called at the end of a dataflow thread to signal the TSU the end of a thread execution and free up thread resources. To reduce simulation polling overhead, the thread is destroyed internally and returns the address of the next thread (if any available) in register %dfr; this slightly deviates from the previously defined syntax (just "**TDESTROY**"). It is a "peeling" optimization dealing with the (common) case when the queue of ready threads is not empty, so that there is no need to return to the polling loop.

- **treadqi** % **res** = \$im: Reads the 64b value stored at the \$im (immediate) offset of the frame of the *self*-thread. This is the immediate form with \$im < 256. For \$im > 255 or variables, use the general form (**TREAD**). The offset immediate is expressed in 64b words (i.e. offset=2 is byte=16).

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 13 of 50

<sup>&</sup>lt;sup>1</sup> Note: this implementation is slightly different from what described in D6.2 where we proposed to write %tid only in case of true condition that is tschedule(&%tid, %ip, %cnd, \$sc).

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

• **twriteqi** %tid, %tval, \$im: Writes the 64b value in register %tval to the location at \$im (immediate) offset of the frame of thread %tid. This is the immediate form with \$im < 256. The offset \$im is expressed in 64b words (i.e. offset=2 is byte=16). For \$im > 255 or variable, use the general form (TWRITE).

• **talloc** and **tfree** are encoded but semantics to be defined.

The above instructions correspond to the instructions (TSCHEDULE, TDESTROY, TREAD, TWRITE, TALLOC, TFREE as introduced in the previous deliverable D6.2 (see Table 1). Additionally, we are currently experimenting with other instructions:

- tschedule %tid = %ip, %sc: Schedules the thread (unconditionally), while the start address is located in register %ip. Register %sc contains the synchronization count. tschedule returns a thread handle in register %tid. By design, we decided to use thread handles expressed on 32 bits; moreover, for efficiency reasons we store such handles on the 32 most significant bits of %tid. In this way, we can do standard address arithmetic on thread handles (e.g., add an offset to obtain the address of an individual element of the thread frame) almost as if they were addresses. This is the general form used with variable sc or sc > 255. For immediate version (sc < 256), tschedulei is more efficient.

- **tschedulei** %tid = %ip, \$sc: Schedules thread (unconditionally) with address in register %ip to be executed. Immediate \$sc holds the synchronization count (0..255). It returns a thread handle in register %tid. The %tid is guaranteed to have bits 0..31 at 0 (see **TWRITE**). Constraint: %tid and %ip must specify the same register identifier (i.e., the same x86\_64 register). For variable sc or sc > 255, the general version (**TSCHEDULE**) is required.

- **tschedulep** %tid = %ip, %sccnd: Schedules thread (conditionally) with address in register %ip to be executed. Register %sccnd packs 'sc' (sync count) and 'cnd' (predicate) as %sccnd = (sc << 1) + cnd. It returns a thread handle in register %tid, or 0 if the predicate is false<sup>1</sup>. The %tid is guaranteed to have bits 0..31 at 0 (see TWRITE). This is the general form used with variable sc or sc>255. For immediate version (sc < 256), tschedulepi is more efficient.

- tschedule %tid = %ip, %sc: Schedules the thread (unconditionally), with the start address in register %ip. Register %sc contains the synchronization count. tschedule returns a thread handle in register %tid. By design, we decided to use thread handles expressed on 32 bits; moreover, for efficiency reasons we store such handles on the 32 most significant bits of %tid. In this way, we can do standard address arithmetic on thread handles (e.g., add an offset to obtain the address of an individual element of the thread frame) almost as if they were addresses. This is the general form used with variable sc or sc > 255. For immediate versions (constant sc < 256), tschedulei is more efficient.

- **tread** % res = % off: Reads the 64b value stored at the offset of % off register of the frame of the same thread. This is the general form of tread (see also **TREADI**) with variable (or > 256) offset.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 14 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

• **treadi** % **res** = \$im: Reads the 64b value stored at the \$im (immediate) offset of the frame of the *self*-thread. This is the immediate form with \$im < 256. For \$im > 255 or variable, use the general form (**TREAD**).

- **twrite** %tloc, %tval: Writes the 64b value from register %tval to the location stored in register %tloc. This is the general form of **TWRITE** (see also **TWRITEI**) with variable frame locations. The %tloc register packs a thread handle (tid) and offset (off), so that %tloc = tid + off. tid is the return value of the tschedule instruction (and its variants) and is guaranteed to have the 32 least significant bits set to 0. Hence, tid and off can be used to construct the thread frame location, by adding the values or doing any other standard address arithmetic.

- **twritei** %tid, %tval, \$im: Writes the 64b value in register %tval to the location at \$im (immediate) offset of the frame of thread %tid. This is the immediate form with \$im < 256. The offset \$im is expressed in bytes and has to be 64b aligned. For \$im > 255 or variable, use the general form (TWRITE). This is just a different way to write the TWRITEQI.

- **tload** % res: Loads the TSU frame values into a locally allocated memory chunk of size % res that is directly accessible by the thread with standard loads and stores. (Depending on the implementation of the TSU, it could be simply a no-op).

- **tstore** % **tloc**, % **ptr**, % **len**: Writes the values in memory starting from address % ptr and length % len to the frame location % tloc. The % tloc register packs a thread handle (tid) and offset (off), so that % tloc = tid + off. The value of tid is the return value of the **TSCHEDULE** instruction (and its variants) and is guaranteed to have the 32 least significant bits set to 0, so that a thread location can be constructed with standard address arithmetic (for example, tid could be the address of the frame).

- **tstoreqi** %tloc, %ptr, \$len: Immediate version of the TSTORE operation, with \$len a 1-256 immediate.

Other instructions are used in the runtime:

- **tpoll** % **dfr**: called within a worker thread, polls the TSU about work to do work (address of the dataflow thread to start) is returned in the register % dfr. Used in the runtime and not in the dataflow program.

- **tinit** %nopr, %pstack: initializes a dataflow worker and sets the "no-operation" function in the register %nopr and a reserved region of memory in register %pstack. The no-operation function is used to optimize the simulation idle polling loop. The reserved stack is used to materialize the local frame (by tload, see above) so that it can be used by standard x86 load and store operation by the compiler. Used in the run-time and not in the dataflow programs.

- **treset** %**rs**, %**rn**: resets the dataflow execution, freeing all threads and preparing for a new execution. The register %rs points to a string in memory of length stored in register %rn (for simulation debugging purposes).

And finally, these instructions are used for debugging and tracing of execution statistics

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 15 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

• **tstamp** %ts = %buf: collects per-core stats (instr, cycles, idles) in the memory pointed to by register %buf and returns the current value of simulation nanos in reg %ts. Can be used to address execution statistics (in a much more precise way than using performance counters) from a guest program.

#### 2.3 New T\* Benchmarks (UNISI)

By exploiting the T\* ISE support for the C-language introduced in the section 2.1, new benchmarks have been implemented for running in the COTSon simulator. The *Matrix Multiplier* benchmark is already available in the COTSon repository, while the *Radix Sort* benchmark is going to be released in the near future.

#### 2.3.1 Matrix Multiplier

The matrix multiplication algorithm chosen for the  $T^*$  C-like implementation is the blocked matrix multiplication version, in which the result matrix  $C = A \cdot B$  is recursively constructed as:

$$C_{ab} = \sum_{c=1}^{s} A_{ac} \cdot B_{cb}$$

where  $C_{ab}$  represents a sub-block of the result matrix. The input matrices A and B are required to be square for simplicity, and defined as:

$$A = \{A_{ij}\} \qquad B = \{B_{ij}\}$$

The input parameters that the algorithm needs for execution are two integers s and np, both required being power of 2:

- s number of rows and columns of the square matrices A, B and C;

- np total number of partitions (blocks).

For example, running the application with s=32 and np=4, will perform a multiplication of 2x2 blocked matrices, in which each block is composed by 16x16 elements. Details on the structure of the dataflow version of this benchmark are reported in Appendix A.

The source code of the matrix multiplier algorithm is available to the TERAFLUX partners in the public SOURCEFORGE website [SF]. We report the code for quick reference in the Appendix A.

#### 2.3.2 Other Benchmarks

A Dataflow version of the Recursive Fibonacci application has been implemented in C using the built-ins introduced in Section 2.2, similarly to the Matrix Multiplier described in previous section.

The well-known *Radix Sort* benchmark, which is one of the kernel application included in the SPLASH-2 suite [Cameron95], has been also developed in the T\* C-like style for our experiments. The implementation of this algorithm is still ongoing because it requires some protection mechanism

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 16 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

for managing concurrent accesses to shared data. Since in the TERAFLUX project the Transactional Memory (TM) is supposed to be adopted for this purpose, the implementation of this benchmark will be completed in the near future by exploiting the new TM feature added by the UNIMAN partner to the COTSon platform.

#### 2.4 Single Node T\* Tests (UNISI)

In order to show the potential of the implementation of T\*, we show here the possibility to collect some statistics (number of Dataflow Threads that are executing, running and waiting) related to the execution of some benchmarks on the modified COTSon platform.

We selected for this sake Matrix Multiplier described in Section 2.2.1 or the Recursive Fibonacci (already introduced and described in previous deliverables D6.1, D6.2) as "pipe-cleaners". The first step has been to code those examples by hand, in order to allow the WP4 to have some simple examples to target the proposed T\* instructions.

On the simulator side, the efforts in this year had been to support properly the execution of the Dataflow Thread (this is coded in the publicly available modules TSU, TSU2, TSU3 on the Source Forge website)

DF Threads can be either waiting to become ready (i.e. their synchronization count has not reached zero), or already in the ready queue, waiting for execution once some core becomes available. In the single node experiments, we varied the number of cores from 1 to 32. In this context, simulations have been successfully performed.

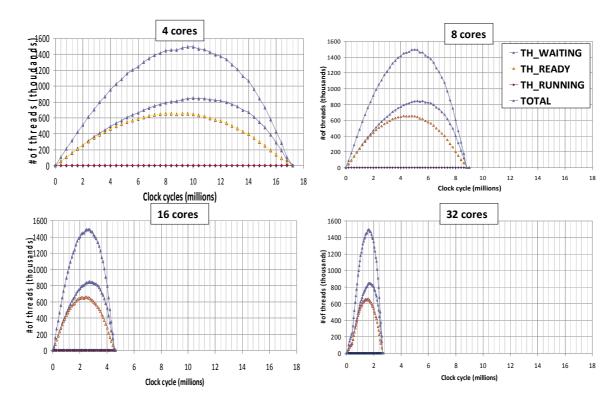

Fig. 2 Fibonacci(35): number of threads in four single-node configurations

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 17 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

In the following, results of the execution of the Fibonacci benchmark are discussed. In particular, Fig. 2 shows the number of threads waiting, ready and running in the system during the execution of the recursive computation of the 35th term of the Fibonacci series, targeting four different single node configurations (4, 8, 16 and 32 cores). The figure highlights two aspects. First, the maximum number of threads created in the system is 1.5M, over all different configurations. Second, the execution time is reduced by a half when the number of cores in the node doubles.

These results show that the COTSon simulator is now able to support the T\* execution model (a dataflow execution model) achieving almost perfect scaling. However, the timing model still has to be tuned up by connecting the existing memory hierarchy timing models of COTSon to the T\* components: such activity is ongoing and briefly described in section 2.3.1. In Fig. 3, we also show a "zoom" of the bottom part of the thread graphs. For each configuration, except for the "startup" and "ending" phases, we observe that there is always a number of running DF-Threads equal to number of cores, demonstrating that the execution paradigm is always able to load the system.

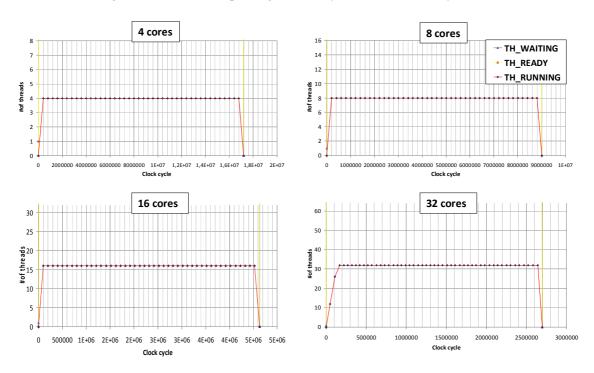

Fig. 3 Fibonacci(35): number of threads (zoomed detail of the previous Figure)

#### 2.4.1 T\* Timing Model

Currently, the TSU implementation already provides functional execution for all T\* instructions. In this section, we describe the implementation efforts for the timing model within the simulator, which assumes the baseline architecture described in D6.3 for the TERAFLUX DTS (Distributed Thread Scheduler).

For explaining the current methodology, we assume the existence of a component still under research in the Architecture workpackage, which is the DF-Frame cache.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 18 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

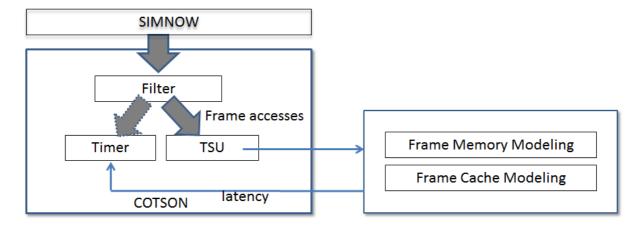

The implementation of the timing model is organized as shown in the Fig. 4. The execution flow is managed as follows:

- During the execution, T\* instructions and memory accesses are dropped from SimNow into COTSon.

- The Filter component filters all T\* memory accesses to DF-Frames by passing them to the TSU in order to model the DF-Frame cache, DF-Frame memory, and all queue structures. All other instructions (i.e., the ones that are part of the regular x86\_64 ISA) are passed directly to the COTSon Timer, which already implement the timing model for non T\* instructions.

- Inside the TSU, the DF-Frame memory and the DF-Frame cache are modeled. For example, we can assume that the access latency to DF-Frame cache is equal to Core Level Cache Hierarchy (CL\$H in the Architectural Template presented in D6.2, Figure 1), and the latency access to physical DF-Frame memory is equal to normal memory access.

- The latency feedback for these accesses in the TSU is passed to the timer in COTson.

Fig. 4 Timing model for the T\* execution

In order to provide the COTSon user with an easy way to model the architecture, for example with the purpose of exploring different configurations which are characterized by different timings, we define the size of DF-Frame cache, DF-Frame memory, queues in a configuration file (e.g. the *tsu.lua* file) which is processed by COTSon.

In the current simulator integration, we have implemented the filtering of T\* instructions and memory accesses into TSU. The next steps will be modeling DF-Frame memory and DF-Frame cache.

# 2.5 Multi-Node T\* Tests (UNISI)

The simulation environment described in section 2.3 created the basis for single node simulations (we decided not to exceed the size of 32 cores per node – current commercial processors like the AMD 6200 encompass 16 cores per processor). In order to simulate systems with a higher number of cores, the number of nodes of the target machine must be increased. In particular, if we want to simulate a

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 19 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

system with say 1024 cores (target for this project as presented in previous deliverables and in particular in D7.2), we may need at least 32 nodes.

Extending COTSon in order to allow many node simulations with T\* support has been performed by UNISI, with the support of HP. Currently, the TSU model is able to perform thread scheduling among many nodes. It has to be tuned up by connecting the timing models of the several existing components (like caches, memory, to the TSU models). We plan to complete the multi-node case in the next year.

In the following, we provide some insights on the framework, and show preliminary results of Fibonacci and Matrix Multiplier running on target machine up to 1024 cores.

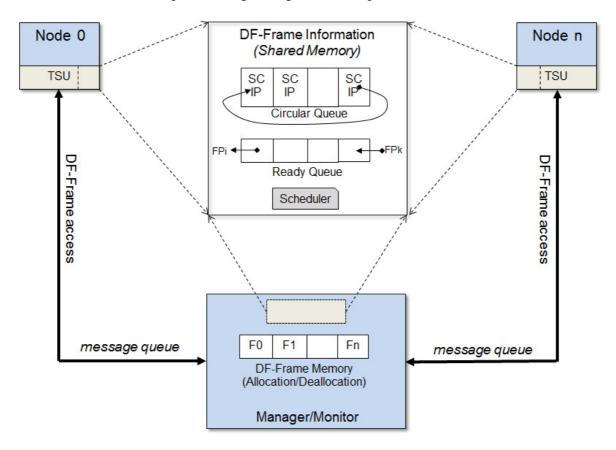

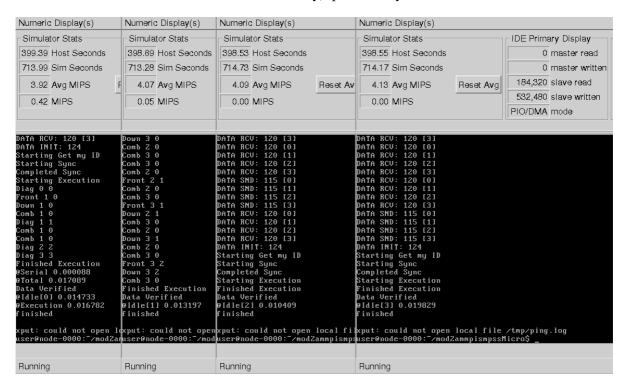

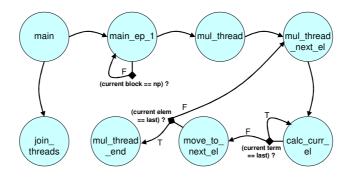

Fig. 5 The structure of the framework for multi-node simulation as it is running on our simulation host.

#### 2.5.1 Framework design

A scheme of the framework for multi-node simulation is shown in Fig. 5. The access to the DF-Frame information among nodes is provided through shared memory allocated on the host machine. Such shared data structures hold 1) a Circular Queue for holding the continuations of created DF-Threads, which are not ready for execution, and 2) the Ready Queue for those threads whose synchronization count has reached zero. A Scheduler is responsible for managing properly these queues. In the current implementation, the Scheduler distributes the ready DF-Threads among nodes following a simple round-robin policy. Nodes can access the DF-Frame Memory through a message queue to a high-level entity we called Manager. Such manager is responsible for allocating-deallocating DF-Frame Memory dynamically.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 20 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

A timing model for the multi-node framework will be designed and developed in the next period, as an extension to the single-node timing model, and is currently under development.

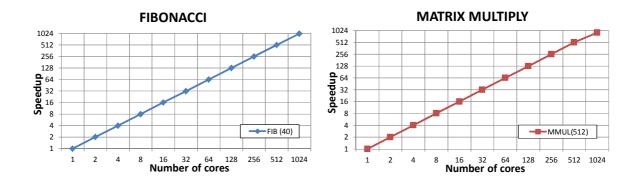

## 2.5.2 Demonstration of multi-node capability of the new distributed scheduler

Fig. 6 shows the speedup – with respect to the single core case – of the execution time for both Fibonacci (computation of 40) and Matrix Multiply (with matrix size of 512). We simulated a number of cores from 1 to 1024, in steps of powers of 2: in the configurations up to 32 cores the systems are single node, from 64 to 1024 cores each simulation run on systems with many nodes, each node hosting 32 cores.

Fig. 6 Multi-node simulation: Fibonacci, with input set to 40, and Matrix Multiply, with matrix size 512x512, partitioned in a number of blocks equal to the number of cores

As we can see, we have reached the ability to simulate the dataflow execution model not only in the single core but also across nodes, without changing the programming model or execution model when passing from the single node case to the multi-node case. Of course, we need to tune up the system in order to evaluate the sensitivity to the availability of resources like bandwidth and memory controllers (as explored initially in the deliverables D2.1, D2.2 regarding the Application work package).

In the case of the matrix multiply benchmark, we start to see some loss of scalability after 512 cores: this is due to the lack of parallelism as we choose too small a data set for this experiment. As a side note, we can see that the simulator is also able to catch such behaviors.

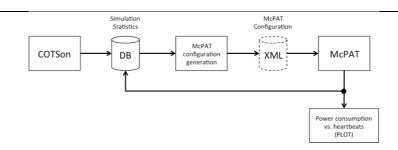

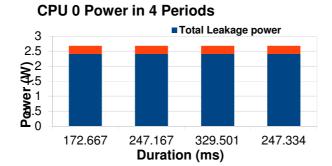

## 2.6 Power estimation using McPAT (UNISI)

Power estimation along with temperature and reliability is an important metric that enables the envisioned architecture to schedule DF-Threads with the aims of improving the overall resiliency of the system. This has been extensively discussed in the previous deliverable D7.3. Here we briefly describe how this mechanism has been extended from an off-line to an on-line methodology. This is necessary to drive the scheduling actions during the program execution.

Looking at the simulation level, power estimation is obtained with the use of an external tool called *McPAT* [MCPAT09]. McPAT has been developed by HP with the ability of estimating power consumption, timing and area of a given microarchitecture. Specifically, McPAT implements an internal model to compute the power consumption based on the activity within the modeled microarchitecture. The activity refers to the instructions executed by the modeled systems, and in

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 21 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

particular to the internal structures that are activated during the execution of each instruction. Combining these statistics with a description of the specific modeled microarchitecture, the tool can estimate static and dynamic power consumption components (e.g., power consumption for the cache memories, power consumption for the cores, etc.), timing and area utilization.

In order to enable the simulated system to schedule DF-threads according to policies that count for the current power consumption, as well as the temperature and the reliability level, the system must be equipped with a power, fault and temperature measurement system. From the perspective of the simulator, this goal can be obtained by integrating the McPAT tool within the COTSon simulator.

#### 2.6.1 Off-line vs. on-line Power estimation

As a first step towards a complete integration, McPAT has been enabled to run at the end of the each *heartbeat*, computing power estimation on a periodic base. Periodic power estimation is obtained storing execution statistics coming from the COTSon simulator at every heartbeat. The heartbeat represents the internal interval used by the simulator to store the statistics (the interval size is not fixed). In the off-line approach, McPAT is run at the end of the COTSon simulation: it processes all recorded heartbeats in sequence at the end of the execution of the program. On the contrary, in the online approach, McPAT is run during the simulation, right after a heartbeat has been produced, while the program is still running.

Fig. 7 shows the current tool chain used to estimate power consumption with an off-line/on-line processing and some first sample of output.

|                      | HEARTBEATS                 | 1—5        |      | 6—10       |      | 11—15      | ;    | 16—20      | )    |

|----------------------|----------------------------|------------|------|------------|------|------------|------|------------|------|

|                      |                            |            |      |            |      |            |      |            |      |

|                      | Core clock                 | 3000       | MHz  | 3000       | MHz  | 3000       | MHz  | 3000       | MHz  |

|                      | Cycles                     | 518001021  | сс   | 741501468  | сс   | 988501962  | сс   | 742001469  | сс   |

|                      | Time                       | 172.667    | msec | 247.167    | msec | 329.501    | msec | 247.334    | msec |

| CDII                 | Subthreshold Leakage power | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    |

| CPU <cpu0>:</cpu0>   | Gate Leakage power         | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    |

|                      | Total Leakage power        | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    |

|                      | Runtime Dynamic power      | 0.269286   | W    | 0.269339   | W    | 0.269316   | W    | 0.269265   | W    |

|                      | Total power                | 2.6738756  | W    | 2.6739286  | W    | 2.6739056  | W    | 2.6738546  | W    |

|                      | •                          | •          |      |            |      | •          |      |            |      |

|                      | Core clock                 | 3000       | MHz  | 3000       | MHz  | 3000       | MHz  | 3000       | MH   |

|                      | Cycles                     | 518001021  | сс   | 741501468  | сс   | 988501962  | сс   | 742001469  | сс   |

|                      | Time                       | 172.667    | msec | 247.167    | msec | 329.501    | msec | 247.334    | mse  |

| CDU1                 | Subthreshold Leakage power |            | W    | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    |

| CPU <cpu1>:</cpu1>   | Gate Leakage power         | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    |

|                      | Total Leakage power        | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    |

|                      | Runtime Dynamic power      | 0.268092   | W    | 0.268093   | W    | 0.268093   | W    | 0.268092   | W    |

|                      | Total power                | 2.6726816  | W    | 2.6726826  | W    | 2.6726826  | W    | 2.6726816  | W    |

|                      | -                          | •          |      |            |      | •          |      |            |      |

|                      | Core clock                 | 3000       | MHz  | 3000       | MHz  | 3000       | MHz  | 3000       | MH   |

|                      | Cycles                     | 518001021  | cc   | 741501468  | cc   | 988501962  | cc   | 742001469  | сс   |

|                      | Time                       | 172.667    | msec | 247.167    | msec | 329.501    | msec | 247.334    | mse  |

| CDII                 | Subthreshold Leakage power | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    |

| CPU <cpu2>:</cpu2>   | Gate Leakage power         | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    |

|                      | Total Leakage power        | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    |

|                      | Runtime Dynamic power      | 0.268092   | W    | 0.268093   | W    | 0.268093   | W    | 0.268092   | W    |

|                      | Total power                | 2.6726816  | W    | 2.6726826  | W    | 2.6726826  | W    | 2.6726816  | W    |

|                      | •                          |            |      |            |      |            |      |            |      |

|                      | Core clock                 | 3000       | MHz  | 3000       | MHz  | 3000       | MHz  | 3000       | ΜH   |

|                      | Cycles                     | 518001021  | сс   | 741501468  | сс   | 988501962  | сс   | 742001469  | сс   |

|                      | Time                       | 172.667    | msec | 247.167    | msec | 329.501    | msec | 247.334    | mse  |

| CPU <cpu3>:</cpu3>   | Subthreshold Leakage power | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    | 2.39913    | W    |

| CPU <cpus>:</cpus>   | Gate Leakage power         | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    | 0.0054596  | W    |

|                      | Total Leakage power        | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    | 2.4045896  | W    |

|                      | Runtime Dynamic power      | 0.268092   | W    | 0.268093   | W    | 0.268093   | W    | 0.268092   | W    |

|                      | Total power                | 2.6726816  | W    | 2.6726826  | W    | 2.6726826  | W    | 2.6726816  | W    |

|                      | •                          |            | •    |            | •    | •          |      |            |      |

|                      | Dynamic                    | 1.073562   | W    | 1.073618   | W,   | 1.073595   | W,   | 1.073541   | W,   |

| All CPU total power: | Leakage                    | 9.6183584  | W    | 9.6183584  | W,   | 9.6183584  | W,   | 9.6183584  | W,   |

| -                    | total                      | 10.6919204 | W    | 10.6919764 | W    | 10.6919534 | W    | 10.6918994 | W    |

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 22 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

Fig. 7 Power estimation sample outputs.

The off-line power estimation process starts with a complete simulation running on the COTSon simulation infrastructure. During the simulation, all the relevant statistics are collected through the internal timer components of the simulator within a SQL local database. The database also contains the main configuration parameters of the simulated machine. Simulation statistics are organized on a per-heartbeat basis. At the end of each heartbeat the content of the database is parsed in order to provide, for each heartbeat, an XML-based configuration file for the McPAT tool. The XML configuration file contains both the main statistics for the current heartbeat, and the machine architecture description. Hence, for each heartbeat, the McPAT tool extracts a power consumption estimation. As shown in, in the case of the on-line power estimation, the set of power estimation values is stored back in the database. This allows the TSU to properly schedule the DF-Threads in order to respect the power/temperature and reliability (see also Section 2.10 in this deliverable and Deliverable D5.3) constraints, and their correlation with power consumption. Similarly to the off-line approach, the XML configuration file is generated by the McPAT configuration generator script at every heartbeat. Finally, in this case the same set of power consumption values can be used to respect the power profile of the simulated machine.

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 23 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

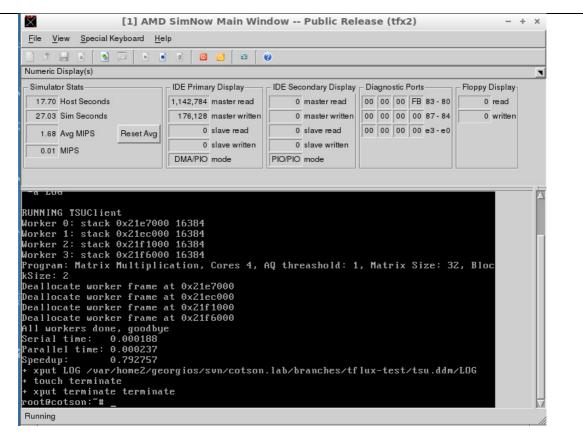

#### 2.7 Execution of User Level DDM on COTSon (UCY)

Within the context of WP7 we have been working on the execution of DDM applications using our user-level DDM TSU runtime. With our first implementation reported earlier we were able to execute on single node COTSon instances. Within this year we have extended the TSU to support execution on distributed systems. Our first attempt to execute on a multi-node COTSon setup did not turn out successful due to problems with the data communication support across multiple COTSon nodes.

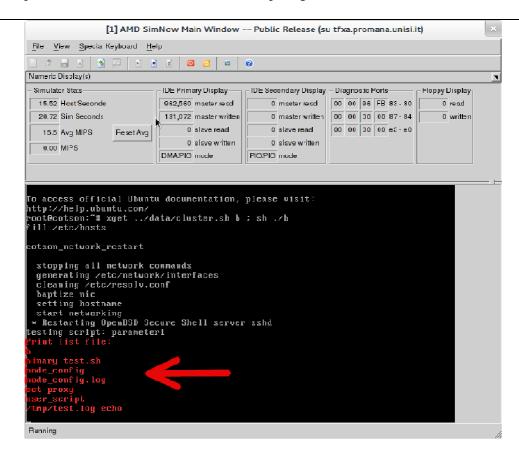

We developed a small benchmark program for the communications layer and we were able to identify that COTSon did not progress when the user sends messages larger than 2KB. To overcome this issue we developed an intermediate communication layer in the TSU network unit that accepts messages of any size and splits them into smaller packets to achieve successful communication. As it is shown in Fig. 8 we have managed to successfully execute a DDM application using 4 nodes on COTSon with the user level TSU.

This configuration was compiled on the tfx2 machine (i.e. one of the simulation hosts provided by UNISI with 48 cores and 256 GB of shared memory), provided by UNISI.

Fig. 8 Running DDM on COTSon, with four nodes

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 24 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

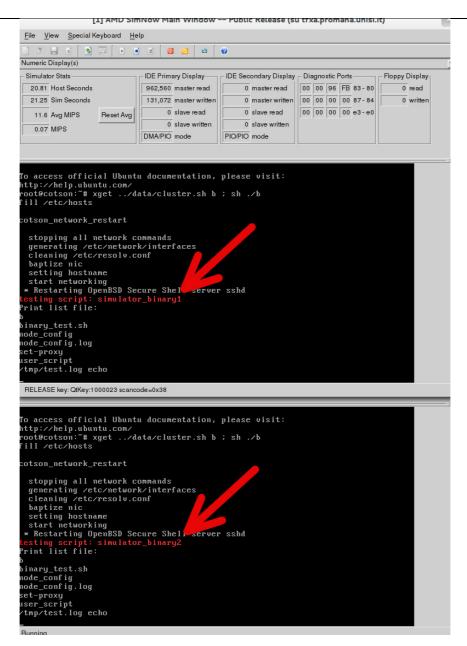

Fig. 9 Blocked Matrix Multiply running on a four cpu machine

# 2.8 Integrating DDM TSU into COTSon (UCY)

As a continuation of the work described in the previous Section, we have integrated the DDM TSU into COTSon by using as template the tsu2 code provided in the TERAFLUX public repository (https://cotson.svn.sourceforge.net/svnroot/cotson/branches/tflux-test/tsu2/) and the TSU++ version of the DDM system. The tsu2 operates as an intermediate API to provide communication between the user application and the TSU unit.

To validate this implementation of the TSU, we have executed the blocked matrix multiply benchmark for 4 workers on a single machine (see Fig. 9).

We have used a single queue to store threads that are ready for execution and a FIFO policy for scheduling. The TSU does not operate in busy-wait mode but instead it is event-driven execution, which seems to make simulation faster. This configuration was compiled on the tfx2 machine (see above).

#### 2.9 GCC Backend and OpenStream Experiments on COTSon (INRIA)

The TERAFLUX backend compiler has been maturing over the course of the third year of the project. It compiles OpenStream programs (data-flow streaming extensions of OpenMP) to T\* intrinsic functions, themselves compiled to the T\* ISA. The code generation pass has been developed as a middle-end pass in GCC 4.7.0, operating on three-address GIMPLE-SSA code. The traditional

Deliverable number: D7.4

Deliverable name: **Report on knowledge transfer and training** File name: TERAFLUX-D74-v10.doc Page 25 of 50

Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

compilation flow is being modified according to a specialized adaptation of the built-in-based, late expansion approach described in D4.2 (first year deliverable). See also **[Li12, Li12b]**. Built-ins are used both to convey the semantics of input and output clauses in streaming pragmas to the compiler middle-end, and to capture the semantics of efficiency languages such as HMPP, StarSs/OMPSs and TFLUX. More details can be found in **[Pop13]** and Deliverable D4.1).

As part of the training and internal dissemination activities, a step by step OpenStream tutorial has been designed and distributed with the OpenStream repository. It consists of a set of 15 thoroughly commented examples illustrating all the features of the language.

The applications ported to OpenStream in WP2 have been distributed together with the OpenStream source code. They have also been packaged as stand-alone benchmarks with multiple data sets and auto-tuning scripts to facilitate the adaptation of the grain of parallelism to the target. The current list of distributed OpenStream programs is: cholesky, fmradio, seidel, fft-1d, jacobi, strassen, fibo, knapsack, matmul, bzip2 (SPEC CPU 2000) and ferret (PARSEC). For some of these programs, multiple versions are provided, to compare data-flow-style, Cilk/join-style, and barrier-style implementations.

All OpenStream applications are supported by the software run-time implementation of T\*. In addition, most applications run on COTSon when compiled using the hardware-ISA branch of the TERAFLUX compiler (i.e., the SourceForge public repository [SF]). The only problematic ones are the Cilk/join and barrier-style variants of the benchmarks that make use of the lastprivate or taskwait constructs of OpenStream. These currently cannot be implemented using T\* (the compiler makes use of scheduling and stack manipulation mechanisms not supported by the tsu2 branch of COTSon). This is not a major issue as the data-flow-style programs compile and run properly, but for completeness and to facilitate the implementation of larger applications, we are working on an extension of the T\* ISA to support these constructs directly.